Lattice SemiconductorのFPGA LCMXO2-256HC(MachXO2シリーズ)は、以下のような利点があります。

- 秋月電子で安く購入できる(在庫限りになってしまったが)

- 外付けのコンフィグレーションROMが不要で、ICひとつで完結する(CPLDのように使える)

日本語資料があまり無いので、書き込んで動かせるようにするまでの一連の手順を解説します。

はじめに

動作確認環境

| 環境 1a | 環境 2b | |

|---|---|---|

| OS | Windows 11 | Windows 10 |

| CPU | AMD, RIZEN 7 3700X | Intel, Core i7-3770 |

| 開発環境 | Diamond v3.12 | Diamond v3.12 |

| 使用言語 | Verilog HDL | Verilog HDL |

| 書込ケーブル | 秋月電子, AE-FT2232 |

- a: Verilog HDLの編集とコンパイルまで

- b: Verilog HDLの編集とコンパイル、FPGAへの書き込みまで

全体の流れ

- Diamondのインストール

- ライセンス認証

- Verilog HDLファイル (***.v)の作成

- 制約ファイル (***.ucf)の作成

- 基板との接続

- プログラムの書き込み

Diamondのインストール

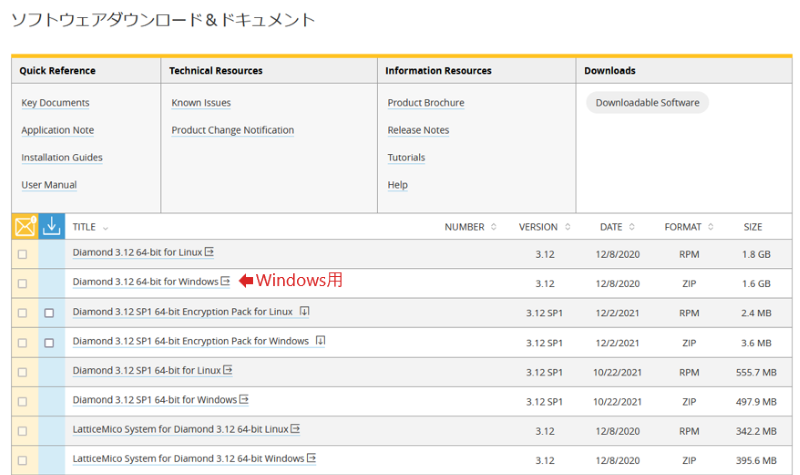

インストーラは、Lattice Diamond設計ソフトウェアのページからDiamond 3.13 64-bit for WindowsなどOSに合わせてダウンロードします。執筆時のバージョンは3.13。

ライセンス認証

まず、Latticeのウェブサイトのアカウント作成ページでアカウントを作成し、サインインします。

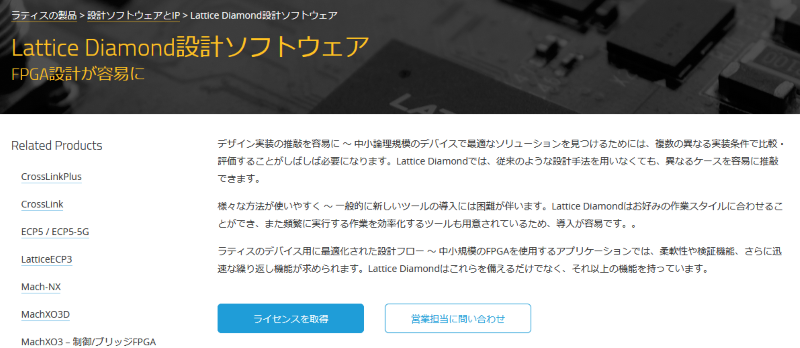

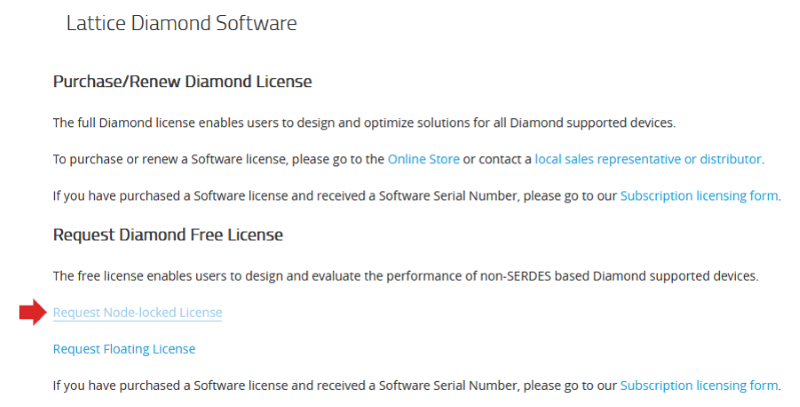

次に、Lattice Diamond設計ソフトウェアのページでライセンスを取得をクリックしてページを移動します。さらに、‘’Request Diamond Free License’’の項目からRequest Node-locked Licenseを選択します。

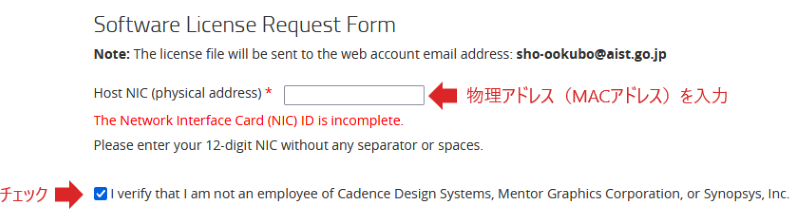

‘’Host NIC (physical address)’‘の入力欄に、PCの物理アドレス(MACアドレス)を12文字で入力(-や:は消す)。Windowsの場合は、コマンドプロンプトでipconfig/allと入力することで調べられます。’‘I verify that…’’にチェックを入れ、下の方にあるGenerate Licenseをクリックすることで、ライセンスファイルがメールで送られてきます。

オプションでいくつかのフリーIPのライセンスも取得できるので、必要がある場合は選択します。私の場合は不要だったのでスルーです。

ライセンスファイルlicense.datは、インストールフォルダの中の~\lscc\diamond\3.12\licenseフォルダなどに置いておきます。Diamondの起動時にライセンスファイルのある場所を聞かれるので、答えると環境変数が設定されます。うまくいかない場合には、手動でシステム変数LM_LICENSE_FILEの値にライセンスファイルのパスを設定。

リモートデスクトップでは、正しい手順を踏んでもライセンスが認証されません。現段階では、Lattice Diamondはリモートデスクトップでは使用できないようです。

新規プロジェクトの作成

- メニューバーから

File→New→Projectの順に選択するか、スタートページ・ビュー左上部のProjectセクションでNew...を選択。 - 指示に従ってデバイス等を選択。プロジェクト生成の際、プロジェクトフォルダは自動生成されないので、あらかじめ作業フォルダを作っておく。

- Projectセクションの入力。

- Name → プロジェクト名(英数字とアンダースコアのみ可)

- Location → プロジェクトフォルダの指定

- Implementationセクションの入力

- Name → インプリメンテーション名。デフォルトはimpl1。

- ソースファイルのインポート。必要なファイル(既存のHDLソースや制約ファイル)を選択する。

Copy source to...にチェックを入れておくと、ファイルをプロジェクトフォルダにコピーしてそれをインポートする。ソースファイルのインポートはプロジェクト作成後でも可。 - デバイスの選択。デバイス、スピードグレード、パッケージを選択。プロジェクト作成後でも変更可。

- 論理合成ツールの選択。デフォルトはLSE (Lattice Synthesis Engine)。プロジェクト作成後でも変更可。

Verilog HDLファイル (***.v) の作成

File Listタブの中のインプリメンテーションファイル名→Input Filesの中に置かれます。ダブルクリックするとエディタが開きます。

制約ファイル (***.lpf) の作成

File Listタブの中のインプリメンテーションファイル名→LPF Constraint Filesの中に置かれる。ダブルクリックするとテキストエディタが開く。

LPF制約ファイルは、Spreadsheet ViewのGUIで各種制約を設定することで書き出せます。ユーザーI/O(RTL記述で宣言されたI/O)のピンアサインをする方法は、以下の通り。

- ポート名に対してピン番号を指定(

Port Assignmentsシートで行う) - ピン番号に対してポート名を指定(

Pin Assignmentsシートで行う)

基板との接続

純正のプログラマケーブル (HW-USBN-2B) は高価なので、最低限の機能を秋月電子のUSB-Serial変換モジュールで実現します。

仕様部材

- 秋月電子, FT2232D USBシリアル2ch変換モジュール

- USBケーブル(Type A-mini B)

- ブレッドボード

- ブレッドボード用ジャンパーワイヤー

接続

AE-FT2232のJTAGのピンアサインは以下の通り。

| AE-FT2232ピン名 | 接続先JTAG信号名 |

|---|---|

| VCCIOA | VCC |

| VCCIOB | VCC |

| AD0 | TCK |

| AD1 | TDI |

| AD2 | TDO |

| AD3 | TMS |

| GND | GND |

各信号のプルアップ/プルダウンは接続先の開発ボード/デバイスに合わせます。ここでは、接続先の基板においてプルアップ/プルダウンされているとして、変換モジュール回路上では特に変更しません。

また、チャンネルAのロジックVCCには接続先の基板の3.3 Vを使用するとして、JP2Aジャンパーを外してVCCIOAに接続先基板のVCC 3.3 Vを繋ぎます。チャンネルBは使用しませんが、同様にJP2Bジャンパーも外してVCCIOBに接続先基板のVCC 3.3 Vに繋いでおきます。

主電源にはUSBバスパワー5 Vを使用するので、JP1ジャンパーは取り付けたままにします。

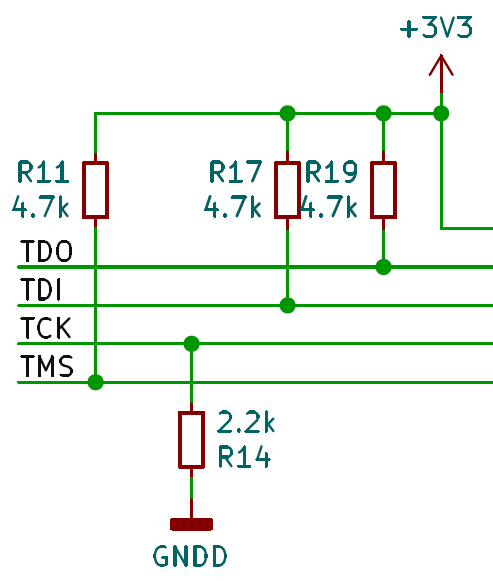

開発ボード/デバイス上では、下図のようにプルアップ/プルダウン抵抗を配します。全てプルアップしてしまったり高めの抵抗を使ってしまったりすると、通信が上手くいかないことがあります。(参考: FTDI2232を用いたJTAG通信 Machxo2書き込み)

ドライバのインストール

FTDIのサイトからドライバを入手。VCP Driversを選択して、OSに対応したドライバをダウンロードして流れに沿ってインストールします。

※ Windows11 x64の場合、2023/1/8時点でのダウンロードファイル名はCDM212364_Setup.zipでした。

インストールが完了すると、USBケーブルでPCに接続したときに、デバイスマネージャー上で2つのCOMポートが認識されます。

Diamondでの設定

モジュールのデータシートでは、保証されるTTLレベルの通信速度は最大3 Mbps。一方、Diamondの初期設定は6 Mbpsなので、Programmerウィンドウ右側のProgrmmer Speed Setting部、TCK Divider Settingで周波数を変更します。Use custom Clock Dividerをチェックし、Divider値を任意の値に変更することによって、周波数を下げられます。

プログラムの書き込み

コンパイル

ProcessタブのExport Filesの下のJEDEC Fileにチェックを入れて、右クリックメニューからRunを実行Map Design→Place & Route Design→Export Filesの順に実行されて、***.jedファイルが生成される

生成されたJEDファイルの書き込み

Tools→Programmerを開くと、JTAGの接続を聞いてくるので、FTDIのデバイスを選択Detect CableでUSB2 - FTUSB-0 (Dual RS232 A Location 0000)の方を選択Use custom Clock Dividerをチェックし、Divider値を任意の値に設定- USB-Serial変換モジュールの仕様上は2以上であればOKですが、試してみたら10分周でようやく書き込めました。ブレッドボードとジャンパーケーブルで接続したのが良くなかったかもしれません。

Device FamilyDeviceFile Nameの項目を正しく設定して、プログラムアイコンをクリックしてコンフィグレーション開始StatusがPASSとなれば完了